# Help Volume

$\ \, {\mathbb C}$  1995-2002 Agilent Technologies. All rights reserved.

Emulation: Hitachi SH7750

### Using the SH7750 Emulation Control Interface

The SH7750 Emulation Control Interface works with an emulation module or emulation probe to give you an emulation interface for Hitachi SH7750 based target systems. Also, with an analysis probe and a logic analyzer, you can make coordinated trace measurements.

Before you begin using the Emulation Control Interface, make sure you have set all of the necessary configuration options (see page 13).

- "At a Glance" on page 10

- "Connecting the Emulator to the Target System" on page 11

- "Configuring the Emulator" on page 13

- "Controlling Processor Execution" on page 19

- "Using Breakpoints" on page 20

- "Displaying and Modifying Registers" on page 24

- "Displaying and Modifying Memory" on page 26

- "Displaying and Modifying I/O" on page 30

- "Downloading an Executable to the Target System" on page 31

- "Coordinating Trace Measurements" on page 48

"Disconnecting from the Emulator" on page 67

"Error/Status Messages" on page 60

"To Use the Command Line Interface" on page 54

"Managing Run Control Tool Windows" on page 53

"Testing Target System Memory" on page 68

Main System Help (see the Agilent Technologies 16700A/B-Series Logic

#### See Also

Analysis System help volume)

Glossary of Terms (see page 87)

### **Related Help**

Setting Up and Starting the Emulation Control Interface (see the Emulation: Setting Up help volume)

Using the SH7750 Emulation Control Interface

### Using the SH7750 Emulation Control Interface

### 1 Using the SH7750 Emulation Control Interface

At a Glance 10

Connecting the Emulator to the Target System 11

To connect to a target system using a debug port 11

To connect the emulator to an analysis probe 12

Configuring the Emulator 13

"Break In" Port 14

"Trigger Out" Port 14

Initialization Timing 15

Hitachi-UDI Connector 16

JTAG Clock Speed 16

Break point at delay slot 17

Memory System Endian Mode 17

To save configuration settings 17

To restore saved configuration settings 18

Controlling Processor Execution 19

Using Breakpoints 20

How hardware breakpoints work 22

How software breakpoints work 23

Displaying and Modifying Registers 24

To display registers 24

To modify register contents 25

Error/Status Messages Address is a duplicate of Breakpoint #\_ 61 Address is not on an instruction (4-byte) boundary 61 Debug Mode Access Error 61 Debugger: memory update 61 Debugger: register update Enable breakpoint failed 62 Hardware breakpoint 62 Memory access failed 62 Software breakpoint: 62 Stepping failed 62 Target power is off 63 Unable to break 63 Unable to modify register: PC=value 63 Unknown break cause 63 Unimplemented opcode/register 63 SH7750 Run Control Tool—New Features in This Version 64 To update firmware 65 Disconnecting from the Emulator 67

| Testing Target System Memory 68           |

|-------------------------------------------|

| Memory Test: 70                           |

| To perform the Basic Pattern test 71      |

| How the Basic Pattern test works 72       |

| To perform the Address Pattern test 73    |

| How the Address Pattern test works 74     |

| To perform the Rotate Pattern test 74     |

| How the Rotate Pattern test works 76      |

| To perform the Walking Ones test 77       |

| How the Walking Ones test works 77        |

| To perform the Walking Zeros test 78      |

| How the Walking Zeros test works 79       |

| To perform the Oscilloscope Read test 79  |

| How the Oscilloscope Read test works $80$ |

| To perform the Oscilloscope Write test 80 |

| How the Oscilloscope Write test works 81  |

| Memory Range 82                           |

| Data Value 82                             |

| Options 82                                |

| To open the Memory Test window 83         |

| Recommended Test Procedure 83             |

# Glossary

### Index

1

Using the SH7750 Emulation Control Interface

### At a Glance

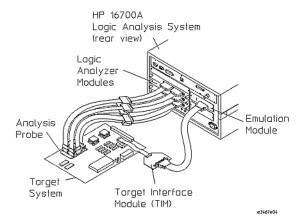

- Logic analysis system Contains measurement modules such as the 16550A State/Timing Logic Analyzer Module. Contains the Emulation Control Interface that controls the emulation module or emulation probe.

- Analysis probe The E8029A analysis probe provides state analysis for the SH7750 processor.

- Emulation module or emulation probe The E3467A SH7750 emulation module/probe connects to a debug port designed into your target system or to the analysis probe—it accesses the debugging facilities built into the SH7750 microprocessor to give you control over processor execution, and easy access to processor registers, target system memory, and I/O.

- Target System Your system using a SH7750 processor.

# Connecting the Emulator to the Target System

You can connect the emulation module or emulation probe directly to a socket on the target system, or you can connect it using a socket built into the analysis probe.

- "To connect to a target system using a debug port" on page 11

- "To connect the emulator to an analysis probe" on page 12

# To connect to a target system using a debug port

In order to connect the emulation module or emulation probe to the microprocessor, a 14-pin debug port must be available on the target system.

To connect the probe to a target system:

- 1. Turn OFF power to the target system and the emulator.

- 2. Plug one end of the 50-pin cable into the emulator.

- 3. Plug the other end of the 50-pin cable into the target interface module.

- 4. Plug one end of the 14-pin cable into the target interface module. Be sure to align pin 1 of the cable to pin 1 on the target connector.

- 5. Plug the other end of the 14-pin cable into the debug port on the target system.

- 6. Turn on the power to the probe.

- 7. Turn on the power to the target system.

#### See Also

The manual for your emulation probe or processor solution.

### To connect the emulator to an analysis probe

A debug port has been designed into the analysis probe. You can connect the emulator to this port.

The Setup Assistant can guide you through the process of connecting both the analysis probe and the emulator.

If you are not using the Setup Assistant, here is a summary of the steps to connect the emulator to the analysis probe:

- 1. Turn OFF power to the target system, logic analysis system, and emulator.

- 2. Connect the analysis probe to the target system as described in the analysis probe or processor solution manual.

- 3. Plug one end of the 50-pin cable into the emulator.

- 4. Plug the other end of the cable into the analysis probe's connector.

- 5. Turn ON power to the emulator.

- 6. Turn ON power to the logic analysis system.

- 7. Turn ON power to the target system.

#### See Also

The Setup Assistant.

The manual for your emulation probe or processor solution.

# Configuring the Emulator

Use the *Setup* window to configure the emulator for your target system.

- 1. Open the Setup window.

- 2. Make the appropriate selections for the probe configuration options you wish to change.

The configuration options are:

- ""Break In" Port" on page 14

- ""Trigger Out" Port" on page 14

- "Initialization Timing" on page 15

- "Hitachi-UDI Connector" on page 16

- "JTAG Clock Speed" on page 16

- "Break point at delay slot" on page 17

- "Memory System Endian Mode" on page 17

#### NOTE:

The "Break In" and "Trigger Out" ports cannot be active at the same time.

The configuration of the emulator is changed immediately when you make a selection.

3. When you have finished changing the configuration options, select *File*, then select *Close*.

#### See Also

- "To save configuration settings" on page 17

- "To restore saved configuration settings" on page 18

- The manual for your emulator or processor solution.

### "Break In" Port

The Break In port allows devices external to the emulator (for example, a logic analyzer's trigger output) to stop user program execution.

Disabled

Rising or falling edges on this port have no effect on the

emulator.

On Rising Edge

Rising edges on this port will cause processor execution to

break into the *monitor*.

This is the proper selection when the port is connected to

the logic analysis system's trigger output.

On Falling Edge

Falling edges on this port will cause processor execution to

break into the *monitor*.

NOTE:

The "Break In" and "Trigger Out" ports cannot be active at the same time.

### "Trigger Out" Port

The Trigger Out BNC port can be used to tell devices external to the emulation probe when processor execution is in the *monitor*.

You can use this port to qualify a logic analyzer clock, so that monitor cycles are not captured.

You can also use this port to signal the target system, for example, so that watchdog timers don't time-out when processor execution is in the monitor.

The options are:

**Always High** Output is always high.

**Always Low** Output is always low.

#### High on Break

Output is high when processor execution is in the monitor.

#### Low on Break

Output is low when processor execution is in the monitor.

NOTE:

The "Break In" and "Trigger Out" ports cannot be active at the same time.

### **Initialization Timing**

**Power-On Reset** The emulation circuitry in SH7750 (Hitachi-UDI) must be initialized at target power-on and may need to be initialized when it is in an unstable condition. You may specify this option if you want to initialize the SH7750 processor and the SH7750 emulation circuitry only when the target power-on is detected.

Target Reset

Choose this option if you want to initialize the emulation circuitry in SH7750 processor when the target power-on or target reset is detected. When the emulation probe/module detects the RESET signal being low, it initializes the emulation circuitry of the SH7750 processor.

**Emulation Reset** Choose this option if you want to initialize the emulation

processor when the target power-on is detected or the emulation reset is requested (by pressing the "reset" button of the interface). The initialization at the emulation reset can not initialize the entire emulation circuitry of the Hitachi-UDI. The SH7750 processor may execute the user program from the reset vector shortly after the Hitachi-UDI reset. This configuration option should not be selected if your user program at the reset vector is not properly implemented.

All Case

Choose this option if you want to initialize the processor when the target power-on is detected, target reset is detected, or emulation reset is requested.

### Hitachi-UDI Connector

This configuration option specifies which connector you are using to connect your emulation probe to the target system.

**Target** Choose this option if your emulation probe/module is

connected to your target board's Hitachi-UDI connector. The /TRST signal will be driven to low by the emulation probe when emulation reset has been issued. (Resets

Hitachi-UDI)

**Analysis Probe** Choose this option if your emulation probe/module is

connected to your analysis probe's Hitachi-UDI connector. The emulation probe does not drive the /TRST signal. You must manually reset your target board when the processor

or the Hitachi-UDI port is in unstable condition.

### JTAG Clock Speed

This configuration option specifies the clock speed at which the emulator communicates with the Hitachi-UDI debug port.

The Hitachi-UDI clock speed is independent of processor clock speed. In general, the default speed of 10.5MHz can be used and provides the best performance. If your target system has additional loads on the Hitachi-UDI lines, or if it does not meet the requirements described in the Emulation for the Hitachi SH7750 user's guide, using a slower Hitachi-UDI clock speed may enable the emulator to work.

The speeds you can specify are:

10.5MHz

5.25MHz

2.63MHz

1.32MH

0.656MHz 0.328MHz

0.164MHz

### Break point at delay slot

This configuration option specifies if setting a software break point at delay slot is allowed.

A software break point at delay slot causes illegal slot exception processing in your program.

**Enable** Setting software break points at any location are allowed

**Disable** When disabled, the emulation module/probe checks if the

instruction immediately before the requested software break point address is a delayed branch. The break point command fails if the instruction was the delayed branch.

# Memory System Endian Mode

Choose the endian mode.

**Big** Choose this option if your program is compiled as big

endian.

**Little** Choose this option if your program is compiled as little

endian.

### To save configuration settings

You can save emulation configuration settings as part of a logic analysis system configuration file. This saves all workspace configurations, including the emulation module and emulation probe configuration settings.

See Also

Saving a New Configuration File (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume)

# To restore saved configuration settings

If you saved emulation configuration settings as part of a logic analysis system configuration file, you can restore them by loading the configuration file. This restores all workspace configurations, including the emulation module and emulation probe configuration settings.

#### See Also

Loading Configuration Files (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume)

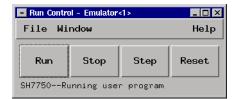

# **Controlling Processor Execution**

Processor execution is controlled using the Run Control window.

- To run the program, select Run.

- To stop program execution, select *Break*.

- To reset the processor, select *Reset*.

- To step a single instruction, select *Step*.

The *status line*, which appears under the run control buttons, shows the current status of the emulator. It shows whether:

- the processor is running the user program,

- the processor is in debug mode;

- there is no power to the target system.

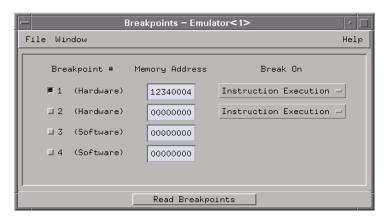

# Using Breakpoints

The Breakpoints window allows you to set breakpoints to stop processor execution when an instruction at a particular address is executed, or when a memory location is written or read.

You can enable up to three hardware breakpoints and up to two software instruction breakpoints.

### To set a breakpoint

- 1. Decide whether you want to set a hardware breakpoint or a software breakpoint.

- 2. Enter an address for the breakpoint in the  $Memory\ Address$  field.

Type the address in hexadecimal format. The address must be on an even boundary; that is, the address must end in 0, 2, 4, 6, 8, A, C, or E. Here are a few examples of valid breakpoint addresses:

000F0100 00002ffc

3. If you are setting a hardware breakpoint, select whether to *Break On Instruction Execution*, *Data Writes*, *Data Reads*, or *Data Reads or Writes* but not instruction fetches.

4. Select the enable/disable toggle button to enable the breakpoint.

A breakpoint is enabled when the button is in:  $\blacksquare$ 1

### To clear a breakpoint

• Select the enable/disable toggle button to disable the breakpoint.

A breakpoint is disabled when the button is out:

Read Breakpoints will display the breakpoints which are currently in effect in the target system. If you have used a debugger with the emulator to set breakpoints, you can use this button to read the breakpoints into the Breakpoints window.

Breakpoints are set or cleared in the target system when you select the enable/disable toggle button. If you change the address of an enabled breakpoint, the new breakpoint address is set in the target system when you move the mouse pointer from the address field. When a new breakpoint is being set in the target system, the mouse pointer will appear as an hourglass for a few moments.

See Also

"How hardware breakpoints work" on page 22

"How software breakpoints work" on page 23

# How hardware breakpoints work

The Hitachi SH7750 processor provides several built-in breakpoints.

Because these breakpoints are implemented by the processor, you can use them to set breakpoints for addresses in ROM.

When a hardware breakpoint is enabled, the processor compares the address of each instruction to be executed with the values in the development mode comparators. If the processor finds a match, it immediately generates an exception.

If your target has an breakpoint exception routine, it will not be used. Instead, the emulator configures the processor to stop immediately when the exception occurs.

# How software breakpoints work

Software breakpoints are implemented by replacing the instruction at the specified address with an interrupt instruction.

When you disable the software breakpoint, the original instruction is restored.

If you *Step* or *Run* from the breakpoint, the original instruction will be executed.

### **Limitations of software breakpoints**

Because software breakpoints write to the breakpoint location, you cannot set software breakpoints in ROM or outside of physical memory. Software breakpoints cannot be used to debug exceptions.

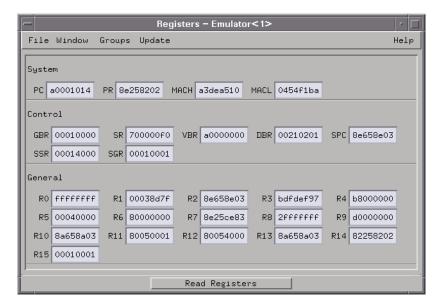

# Displaying and Modifying Registers

The Register window lets you display and modify the contents of processor registers.

- "To display registers" on page 24

- "To modify register contents" on page 25

The Emulation Control Interface displays groups (also called "classes") of related registers.

### To display registers

- To add a group of registers to the display, select the group from the *Groups* menu.

- To remove a group of registers from the display, select the group from the *Groups* menu.

- To move a group to the bottom of the display, remove the group then add it

again.

• To read the register values from the processor, select *Read Registers*.

The registers displayed vary according to the target processor.

The Registers window will be updated as the processor runs. If you want to disable this automatic updating, change *Freeze Window (No)* to *Freeze Window (Yes)* in the Update menu.

# To modify register contents

- 1. Display the group of registers that contains the register whose contents you wish to modify.

- 2. Select the value field you wish to modify. The underline cursor indicates the field that has been selected.

- 3. Type the new register value.

The new value is actually written as soon as:

- you press the Enter (or Return) key, or

- the mouse pointer leaves the entry field.

# Displaying and Modifying Memory

- "To display memory" on page 26

- "To modify a memory location" on page 27

- "To fill a range of memory locations" on page 27

- "To display memory in mnemonic format" on page 28

- "Addresses" on page 29

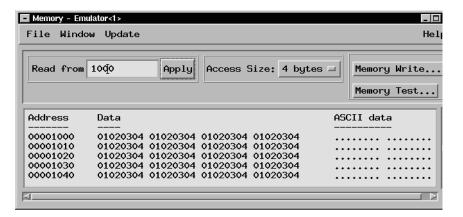

### To display memory

- 1. Open the Memory window.

- 2. Specify the display format by selecting the appropriate *Access Size* and *Base of Data* options.

- 3. Enter the address (see page 29) you wish to read in the *Read from* field, and select *Apply*.

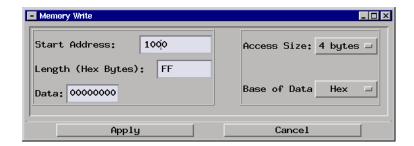

### To modify a memory location

- 1. Open the Memory window.

- 2. Select Memory Write....

- 3. Enter the address (see page 29) of the location in the Start Address field.

- 4. Enter a length of 1. (Entering a larger value will fill multiple memory locations with the value.)

- 5. Enter the value that you want to write in the *Data* field.

- 6. Specify the size of the memory location and the format of the value you wish to enter by selecting the appropriate *Access Size* and *Base of Data* options.

- 7. Select Apply.

# To fill a range of memory locations

- 1. Open the Memory window.

- 2. Select *Memory Write...*

- 3. Specify the size of the memory locations and the format of the value you wish to enter by selecting the appropriate *Access Size* and *Base of Data* options.

- 4. Enter the address (see page 29) of the first location in the *Start Address* field, enter the number of addresses to be written with the value in the *Length* field.

- 5. Enter the value that you want to write in the *Data* field.

- 6. Select Apply.

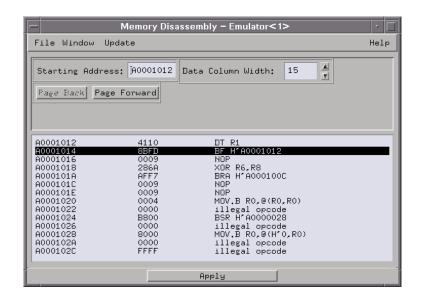

### To display memory in mnemonic format

Open the Memory Disassembly window.

Memory is disassembled beginning at the current program counter value.

The line corresponding to the program counter will be highlighted.

### To display memory beginning at another address

- 1. Enter the first address (see page 29) to disassemble in the Starting Address field.

- 2. Select the appropriate Data Column Width.

- 3. Select Apply.

### **Scrolling**

Page Forward and Page Back let you scroll the displayed memory locations. You cannot page back beyond the starting address.

# Program counter tracking

If you step the processor or run and then stop, the highlighted line will track the current program counter.

If you do not want the highlighted line to track the program counter, select *Freeze Window (No)* in the Update menu.

### Addresses

Enter all addresses in hexadecimal format.

Examples:

ABCDEF89 00000100 0040

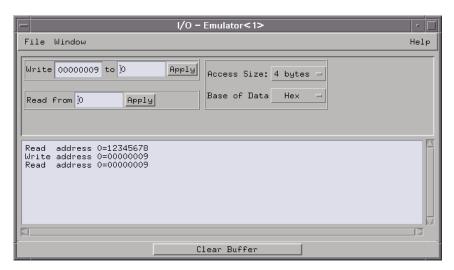

# Displaying and Modifying I/O

### To display I/O locations

- 1. Open the I/O window.

- 2. Specify the display format by selecting the appropriate *Access Size* and *Base of Data* options.

- 3. Enter the address you wish to read in the *Read from* field, and select *Apply*.

Clear Buffer empties the contents of the I/O window.

### To modify an I/O location

- 1. Open the I/O window.

- 2. Specify the size of the I/O location and the format of the value you wish to enter by selecting the appropriate *Access Size* and *Base of Data* options.

- 3. Enter the value that you want to write in the *Write* field, enter the address of the location in the *to* field, and select *Apply*.

# Downloading an Executable to the Target System

Use the Load Executable window to load executables (or other data) into your target system. You can load your data into RAM or into flash ROM.

- "To download into target RAM" on page 32

- "To download into target flash ROM" on page 34

- "To erase flash ROM" on page 35

NOTE:

You must always erase flash ROM before you program it.

NOTE:

Programming and erasing flash ROM may take a very long time on some processors. Additionally, Intel Quick-Pulse parts take longer to erase than others. The following examples show how long it took to perform various flash tasks on different processors. Your times will be different from the times in the examples. Use the Load Executable window to program or erase flash ROM only if these measurements are acceptable for your needs.

<sup>\*</sup> To program a 1 megabyte file using AMD 5 Volt parts:

<sup>\*</sup> CPU32: 5 minutes \* MPC860: 20 minutes \* PowerPC 603e: 1 hours, 30 minutes

<sup>\*</sup> To erase 1/2 megabyte Intel Quick-Pulse part:

<sup>\*</sup> CPU32: 2 minutes

#### **Downloading an Executable to the Target System**

Note that Intel Quick-Pulse parts always take longer to erase than other parts. PowerPC 60x always takes longer to program than Motorola MPC860 or CPU32.

### To download into target RAM

- 1. Save the executable where the logic analysis system can read it (see page 33).

- 2. Open (see page 51) the Load Executable window.

- 3. Select the *Load Executable* operation. The parts of the window relating to flash ROM programming will be "grayed out".

- 4. Select the format (see page 33) of the file.

- 5. Change the Access Size option, if necessary.

- 6. If you chose the Motorola S-Records format or the ELF Object format, change the *Set PC after load* option, if necessary. If this option is selected (the button is in), the PC will be set to the execution start address, if it is specified in the file.

- 7. Enter the name of the file to load.

- 8. Select Apply.

When the file has been successfully loaded, "load completed" message will be displayed.

#### See Also

- "To access a file from the logic analysis system" on page 33

- "To choose a file format" on page 33

- "Error messages while downloading files" on page 36

<sup>\*</sup> To erase 2 megabyte AMD 5 Volt parts:

<sup>\*</sup> MPC860: 10 seconds \* PowerPC 603e: 5 seconds

### To access a file from the logic analysis system

You need to save the executable file where the logic analysis system can read it.

If you will be downloading many files, you should NFS-mount the file system (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume) of the computer where you are compiling your program. If you do this, you can directly access your executable, regardless of how big it is, as soon as it is compiled or assembled. Mounting the file system may require the help of a system administrator.

You can also copy the file (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume) from a floppy disk to the logic analysis system's hard disk. If the file is too big to fit on the floppy disk, use PKZIP to compress the file, then uncompress (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume) the file using the File Manager.

### To choose a file format

You can choose one of the following file formats:

- Motorola S-records Most compilers for Motorola microprocessors can generate Motorola S-records. (see page 38) This file format represents the binary data as hexadecimal numbers in a ASCII file. Each record in the file includes a load address for the data in the record.

- Intel Extended Hex The Intel extended hex (see page 39) format represents binary data as hexadecimal numbers in a ASCII file. Each record in the file includes a load address for the data in the record.

- Plain binary If you choose *Plain binary*, the data in the file will be copied directly to the target system. Because plain binary files contain no information about where to load the file in memory, you must enter a start address.

- ELF Object Many compilers generate ELF Object files. This option will allow statically linked ELF images to be loaded into the target memory.

#### **Downloading an Executable to the Target System**

Dynamically linked ELF shared libraries cannot be loaded with this option.

If your executable is not in one of these formats, recompile, reassemble, or relink your program with the appropriate options to generate one of these formats.

#### See Also

- "Details of the Motorola S-record format" on page 38

- "Details of the Intel extended hex format" on page 39

### To download into target flash ROM

- 1. Save the executable where the logic analysis system can read it (see page 33).

- 2. Open (see page 51) the Load Executable window.

- 3. Select the *Program Flash* operation. The part of the window relating to "Erase Flash" will be "grayed out."

- 4. Select the *Algorithm* (see page 40) used by your flash ROM part.

- 5. Select the *Bus Width* of the data bus connected to your part.

- 6. Select the *Device Width* of your part.

- Notice that the *Bus Width* refers to your target system, but that *Device Width* refers to the flash ROM part.

- 7. Enter the *ROM Start Address*. This is the first address in memory which maps to your flash ROM part.

- 8. Enter the ROM Size.

This is the total size (in bytes, hexadecimal) of the ROM address space. For example, if you have four flash parts which are each 1 MB in size, enter 400000.

The emulator will not write to or erase addresses outside of the range [Start Address .. Start Address + ROM Size]. If your executable file contains data for both ROM and RAM addresses, only the data corresponding to the flash ROM addresses will be written.

9. If the flash ROM has not been erased, erase (see page 35) it.

- 10. Select the format (see page 33) of the file.

- 11. Change the *Access Size* option, if necessary.

- 12. If you chose the Motorola S-Records format or the ELF Object format, change the *Set PC after load* option, if necessary. If this option is selected (the button is in), the PC will be set to the execution start address, if it is specified in the file.

- 13. Enter the name of the file to load.

- 14. Select *Apply*.

When the file has been successfully loaded, "Load completed" message will be displayed.

#### See Also

- "To choose a flash algorithm" on page 40

- "To erase flash ROM" on page 35

- "To access a file from the logic analysis system" on page 33

- "To choose a file format" on page 33

- "Error messages while downloading files" on page 36

### To erase flash ROM

- 1. Open (see page 51) the Load Executable window.

- 2. Select *Flash Erase*. The "Load Options" part of the window will be "grayed out."

- 3. Select the *Algorithm* (see page 40) used by your flash ROM part.

- 4. Select the *Bus Width* of the data bus connected to your part.

- 5. Select the *Device Width* of your part.

Notice that the *Bus Width* refers to your target system, but that *Device Width* refers to the flash ROM part.

6. Enter the *ROM Start Address*. This is the first address in memory which maps to your flash ROM part.

#### **Downloading an Executable to the Target System**

7. Enter the ROM Size.

This is the total size (in bytes, hexadecimal) of the ROM address space. For example, if you have four flash parts which are each 1 MB in size, enter 400000.

The emulator will not erase addresses outside of the range [Start Address .. Start Address + ROM Size].

8. If the *Erase chip* button label is not "grayed out", select the button to erase the whole part.

The Intel Quick-Pulse and AMD 12 Volt Embedded algorithms only allow erasing of the who part. The Intel Auto algorithm requires one or more sectors of the part to be specified for erasing. The AMD 5 Volt Embedded algorithm allows you to choose whether to erase the whole part or just specific sectors.

9. If you did not select *Erase chip*, enter the address of each sector you want to erase.

You may erase up to four sectors at once. To erase more than four, simply enter the additional sectors after applying the erase function with the first four.

# Error messages while downloading files

- AMD5 Volt algorithm requires either the "Erase chip" option or more sectors to be specified. If you do not select *Erase chip*, then you must select one or more sector addresses to erase. To select a sector to erase, select the box beside one of the sectors then enter a hex number for the address of the sector.

- Bad Load Address The start address which you entered for the plain binary file is invalid.

- Bad ROM Size. Specify a hex number. The number in the field is invalid. Re-enter a hexadecimal value.

- Bad ROM Start Address. Specify a hex number. The number in the field is invalid. Re-enter a hexadecimal value.

- Bad Sector Address. Specify a hex number. The number in the field is

invalid. Re-enter a hexadecimal value.

- Checksum errors found in non-data records. Checksum errors were found in one or more non-data records, but no errors were found in the data records. The data records were loaded.

- ELF file has no object image to load. Load not completed. This means we found a valid ELF Object file, but the target image was not included with the file. With no target image, we had nothing to load.

- File could not be opened. The executable file could not be opened. Check that the file exists, that the file permissions allow reading, and that the file is a data file and not a directory.

- File not in Intel Extended Hex file format. Load not completed, check format selection. Check that you have selected the correct file format button. If you still get this message, compare the file to the description in "Details of the Intel extended hex format" on page 39.

- File not in Motorola S-Record file format. Load not completed, check format selection. Check that you have selected the correct file format button. If you still get this message, compare the file to the description in "Details of the Motorola S-record format" on page 38.

- Flash ROM memory access failure. The emulator is unable to access ROM memory at the specified location. Check that the *Start Address* and *ROM Size* values are correct. Also, check that your target system has been set up correctly. For example, check that the chip select registers are set to allow access to the ROM memory.

- Intel Auto algorithm requires one or more sectors to erase. The Intel Auto algorithm does not support "bulk erasing" the entire part. Select one or more sector addresses to erase. To select a sector to erase, select the box beside one of the sectors then enter a hex number for the address of the sector.

- Load Failed: binary data load exceeds memory boundary. If the plain binary file were to be loaded at the the start address which you entered, some of the data would be written past the end of memory. Check the start address, then check that the file has a size that will fit in your target system's memory.

- Load failed: Checksum Errors found in data record(s). Checksum errors were found in one or more data records. The load was aborted. Generate a new executable file.

### **Downloading an Executable to the Target System**

- Load Failed: ELF file has a format problem. ELF file has been altered in some way that we can no longer recognize it as an ELF file.

- Load Failed: Refer to Status/Error Log window. The Status/Error Log window will contain additional information about the errors that occurred.

- Non-ROM data encountered and ignored. This message means that a "Program Flash" operation was performed using a file which contained both data within the ROM address range and data outside the ROM address range. The ROM address range is determined by the values you entered: [Start Address .. Start Address + ROM Size]. Every byte in the file which is within the ROM address range was written to ROM; the data outside this range was ignored. If the data file should not have contained data for addresses outside of the ROM, check that the *Start Address* and *ROM Size* values are correct.

- Program AMD12V not erased. A message similar to this results from attempting to program ROM which has not been erased first. Erase the ROM before programming.

- Sector not erased outside of ROM range. A sector address for the "Erase Flash" operation was outside the range [Start Address .. Start Address + ROM Size]. All sectors specified to be erased must reside within the ROM address range. Check the ROM address range and the sector address.

## Details of the Motorola S-record format

An S-Record file has the following format:

```

[$$[module_record]

symbol records

$$[module_record]

symbol records

$$]

header_record

data_records

record_count_record

terminator record

```

Each record in the file consists of

• Record type (2 characters)

- S0 Header record

- S1,S2,S3 Data record

- S5 Record count

- S7,S8,S9 Terminator

- Record length, in bytes, not including the record type field (2 characters)

- Load address (2-8 characters)

- The data, represented in hexadecimal. (length determined by the record length field)

- Checksum, calculated as the 1's complement of all bytes in the record, not including the record type field (2 characters)

When downloading a file, anything before the header (such as any module or symbol records) is ignored. All optional records are ignored.

### Example

Here is an example of an S-Record file:

S00600004844521B S20700665400B24C40 S20500665F45F0 S21400600033FC000A0000B24C202F00046C0622006D ... S2060066424E758E S50300728A S80400624455

# Details of the Intel extended hex format

Each record in the file consists of

- A colon (:) (1 character)

- Number of bytes in the data field (2 characters)

- Load address (4 characters)

- Record type (2 characters)

- 00 Data

### **Downloading an Executable to the Target System**

- 01 End of file

- 02 Extended segment address (bits 4-19 of a segment base address)

- 03 Start segment address

- 04 Extended linear address (the upper 2 bytes of a data load address)

- 05 Start linear address

- The data, represented in hexadecimal. (length determined by the record length field) For the extended address record types, the data consists of 4 characters representing the appropriate bits of the address.

- Checksum, calculated as the 2's complement of the sum of all of the bytes in the record after the colon (2 characters)

When downloading a file, only record types 00, 01, 02, and 04 are parsed. Any additional records (such as any module or symbol records) before the data records are ignored.

## **Example**

Here is an example of a data record followed by an end of file record:

- :20000000F00100230B340C4510561B6720782B892CAB30BC40CD4CD E50EF60F06C01701290

- :20002000AC230101112321453167418951AB61CDF1EF7121D001C01 F08F9090F18F7190660

- :2000400028F5290438F3390248F1490058FC590D68FE690F78FA790 988109812A834B865A7

- :20006000C867D889E89A8180A1E0E0ABE1464B00AB00AB21AB32AB4 3AB54AB65AB76AB874B

- :20008000AB98AB299C309C819CF29CE39CC49CB59CD69CA79C18BBF F9B38EC0CEC0DEC0EC1

- :2000A000EC0FEC86EC8AEC8BEC8CEC8DEC87EC08EC04EC00EC01EC0 2EC03EC06EC07EC8F88

- :0A01A000000D720000D780030004

- :0000001FF

# To choose a flash algorithm

In the Flash Options section of the Load Executable window, you need to select the algorithm which will be used to program or erase your flash ROM part.

The supported algorithms are:

- AMD 5 Volt Embedded

- AMD 12 Volt Embedded

- Intel Auto

- Intel Quick-Pulse (AMD FlashRite)

If you do not know which algorithm your part uses:

• Look for your part in the "Table of Algorithms Used by Common Flash Parts" on page 41.

If your part is listed in the table, select the algorithm listed for your part. If your part is not listed, but you know that it is a new component belonging to one of the listed families, select the algorithm listed for the parts in the family.

- Check the manufacturer's literature to see if one of the supported algorithms is mentioned.

- "Table of Algorithms Used by Common Flash Parts" on page 41

- "Table of Unsupported Flash Parts" on page 47

## **Table of Algorithms Used by Common Flash Parts**

Choose the manufacturer of your flash ROM part:

- "Table of Algorithms Used by AMD Flash Parts" on page 42

- "Table of Algorithms Used by Fujitsu Flash Parts" on page 46

- "Table of Algorithms Used by Hitachi Flash Parts" on page 45

- "Table of Algorithms Used by Intel Flash Parts" on page 43

- "Table of Algorithms Used by Micron Flash Parts" on page 46

- "Table of Algorithms Used by Mitsubishi Flash Parts" on page 45

- "Table of Algorithms Used by SGS-Thomson Flash Parts" on page 46

- "Table of Algorithms Used by Sharp Flash Parts" on page 47

- "Table of Algorithms Used by TI Flash Parts" on page 45

#### See Also

Information regarding the algorithm used by the listed parts is based on the manufacturer's specifications.

See Also

• "Table of Unsupported Flash Parts" on page 47

# Table of Algorithms Used by AMD Flash Parts

| FAMILY                     | Part                                                                         | Algorithm                                                                                                       |

|----------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| -<br>AMD 12V Bulk Erase    | Am28F256<br>Am28F512<br>Am28F010<br>Am28F020                                 | Intel Quick-Pulse<br>Intel Quick-Pulse<br>Intel Quick-Pulse<br>Intel Quick-Pulse                                |

|                            | Am28F010A                                                                    | AMD 12V Embedded<br>AMD 12V Embedded<br>AMD 12V Embedded<br>AMD 12V Embedded                                    |

| - AMD 5V only Sector erase | Am29F010<br>Am29F100T<br>Am29F100B<br>Am29F002T                              | AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded                                                           |

|                            | Am29F002T<br>Am29F002B<br>Am29F002NT<br>Am29F002NB<br>Am29F200T<br>Am29F200B | AMD 5V Embedded |

|                            | Am29F040<br>Am29F400AT<br>Am29F400AB<br>Am29F400BT<br>Am29F400BB             | AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded                     |

|                            | Am29F080<br>Am29F800T<br>Am29F800B<br>Am29F800BT<br>Am29F800BB               | AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded                     |

|                            | Am29F016<br>Am29F017                                                         | AMD 5V Embedded<br>AMD 5V Embedded                                                                              |

| - AMD 3V only Sector Flash           | Am29DL800T<br>Am29DL800B                                                                        | AMD 5V Embedded<br>AMD 5V Embedded                                                                                              |

|--------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                      | Am29LV002T<br>Am29LV002B<br>Am29LV200T                                                          | AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded                                                                           |

|                                      | Am29LV200B                                                                                      | AMD 5V Embedded                                                                                                                 |

|                                      | Am29LV004T<br>Am29LV004B<br>Am29LV400T<br>Am29LV400B                                            | AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded<br>AMD 5V Embedded                                                        |

|                                      | Am29LV081<br>Am29LV008T<br>Am29LV008B<br>Am29LV800T<br>Am29LV800B<br>Am29LV800BT<br>Am29LV800BB | AMD 5V Embedded |

|                                      | Am29LV160BT<br>Am29LV160BB                                                                      | AMD 5V Embedded<br>AMD 5V Embedded                                                                                              |

|                                      |                                                                                                 |                                                                                                                                 |

| AMD 2.2V only Sector<br>Sector Flash | Am29LL800T<br>Am29LL800B                                                                        | AMD 5V Embedded<br>AMD 5V Embedded                                                                                              |

| -                                    |                                                                                                 |                                                                                                                                 |

# **Table of Algorithms Used by Intel Flash Parts**

| FAMILY                                    | Part                 | Algorithm                |

|-------------------------------------------|----------------------|--------------------------|

| -<br>Intel High Performance<br>Fast Flash | 28F016XD<br>28F016XS | Intel Auto<br>Intel Auto |

| Intel FlashFile                           | DD28F032SA           | Intel Auto               |

|                                           | 28F016SA<br>28F016SV | Intel Auto<br>Intel Auto |

# Chapter 1: Using the SH7750 Emulation Control Interface

# **Downloading an Executable to the Target System**

|                                  | 28F008SA<br>28F008SA-L                                                       | Intel Auto<br>Intel Auto                                                         |

|----------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Intel Boot Block                 | 28F001BX-T/B<br>28F001BN-T/B                                                 |                                                                                  |

|                                  | 28F002BL-T/B<br>28F002BL-T/B<br>28F002BC                                     | Intel Auto                                                                       |

|                                  | 28F200BX-T/B<br>28F200BL-T/B                                                 | Intel Auto                                                                       |

|                                  | 28F400BX-T/B<br>28F004BX-T/B<br>28F400BL-T/B<br>28F004BL-T/B                 | Intel Auto<br>Intel Auto                                                         |

| -                                |                                                                              |                                                                                  |

| Intel SmartVoltage<br>Boot Block | 28F800BV-T/B<br>28F008BV-T/B<br>28F800CV-T/B<br>28F800CE-T/B<br>28F008BE-T/B | Intel Auto<br>Intel Auto<br>Intel Auto                                           |

|                                  | 28F400BV-T/B<br>28F004BV-T/B<br>28F400CV-T/B<br>28F400CE-T/B<br>28F004BE-T/B | Intel Auto<br>Intel Auto<br>Intel Auto                                           |

|                                  | 28F200BV-T/B<br>28F002BV-T/B<br>28F200CV-T/B                                 | Intel Auto                                                                       |

| -<br>Intel Bulk erase            | 28F020<br>28F010<br>28F512<br>28F256A                                        | Intel Quick-Pulse<br>Intel Quick-Pulse<br>Intel Quick-Pulse<br>Intel Quick-Pulse |

| _                                |                                                                              |                                                                                  |

# Table of Algorithms Used by Mitsubishi Flash Parts

| FAMILY          | Part                    | Algorithm                              |

|-----------------|-------------------------|----------------------------------------|

|                 |                         |                                        |

| -<br>Mitsubishi | M5M28F101<br>M5M28F102A | Intel Quick-Pulse<br>Intel Quick-Pulse |

|                 | M5M28F800<br>           | Intel Auto                             |

# **Table of Algorithms Used by TI Flash Parts**

| FAMILY | Part                                                                                                                                                                   | Algorithm                                                                    |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| -      |                                                                                                                                                                        |                                                                              |

| TI     | TMS28F010A TMS28F010B TMS28F512A TMS28F210 TMS28F020 TMS28F040 TMS28F400BZT TMS28F400BZB TMS28F200BZT TMS28F200BZB TMS28F200BZB TMS28F200AXY TMS28F200AXY TMS28F200AXY | Intel Auto |

|        |                                                                                                                                                                        |                                                                              |

# Table of Algorithms Used by Hitachi Flash Parts

| FAMILY  | Part    | Algorithm         |

|---------|---------|-------------------|

|         |         |                   |

| Hitachi | 28F4001 | Intel Quick-Pulse |

|         | 28F101  | Intel Quick-Pulse |

|         |         |                   |

See Also

• "Table of Unsupported Flash Parts" on page 47

# Table of Algorithms Used by SGS-Thomson Flash Parts

| FAMILY      | Part             | Algorithm                |  |

|-------------|------------------|--------------------------|--|

| -           |                  |                          |  |

| SGS-Thomson | 28F410<br>28F420 | Intel Auto<br>Intel Auto |  |

|             |                  |                          |  |

# Table of Algorithms Used by Fujitsu Flash Parts

| FAMILY       |   |      |           | Part                                                                                                                                      | Algo                                    | orit                                                               | hm                                           |

|--------------|---|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------|----------------------------------------------|

| -<br>Fujitsu | 5 | Volt | Operation | MBM29F002T/B MBM29F002ST MBM29F002SB MBM29F200TA MBM29F200BA MBM29F040A MBM29F400TA MBM29F400BA MBM29F400BA MBM29F016 MBM29F016 MBM29F017 | AMD | 5 V<br>5 V<br>5 V<br>5 V<br>5 V<br>5 V<br>5 V<br>5 V<br>5 V<br>5 V | Embedded<br>Embedded<br>Embedded<br>Embedded |

| -<br>Fujitsu | 3 | Volt | Operation | MBM29LV002T/B MBM29LV200T/B MBM29LV004T/B MBM29LV400T/B MBM29LV008T/B MBM29LV800T/B                                                       | AMD<br>AMD<br>AMD<br>AMD                | 5V<br>5V<br>5V<br>5V                                               | Embedded<br>Embedded<br>Embedded             |

# Table of Algorithms Used by Micron Flash Parts

| FAMILY              | Part                              | Algorithm                        |  |

|---------------------|-----------------------------------|----------------------------------|--|

| - Micron Boot Block | MT28F002<br>MT28SF002<br>MT28F200 | Intel Auto Intel Auto Intel Auto |  |

|                            | MT28SF200<br>MT28F004<br>MT28SF004ET<br>MT28SF400<br>MT28SF400<br>MT28SF400ET<br>MT28(S)F008<br>MT28F008<br>MT28SF008 | Intel Auto |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| -<br>Micron Sectored Erase | MT28(S)F116                                                                                                           | Intel Auto                                                                                                                                     |

|                            | MT28F161<br>MT28SF161                                                                                                 | Intel Auto Intel Auto                                                                                                                          |

|                            |                                                                                                                       |                                                                                                                                                |

# **Table of Algorithms Used by Sharp Flash Parts**

| FAMILY | Part          | Algorithm  |

|--------|---------------|------------|

|        |               |            |

| -      |               |            |

| Sharp  | LH28F004SU-LC |            |

|        | LH28F008SA    | Intel Auto |

|        | LH28F016SU    | Intel Auto |

|        |               |            |

| _      |               |            |

# **Table of Unsupported Flash Parts**

The following parts cannot be programmed by the emulator:

| FAMILY                      | Part     |

|-----------------------------|----------|

| Atmel<br>Hitachi<br>Toshiba | HN28F101 |

|                             |          |

# **Coordinating Trace Measurements**

If you are using a logic analyzer (and perhaps an analysis probe) along with an emulation probe to debug your target system, you can coordinate the logic analyzer trace measurements with the execution of your target processor.

- "To break execution on a trigger" on page 48

- "To trigger an analyzer on a break" on page 49

- "To omit monitor cycles from the trace" on page 50

# To break execution on a trigger

#### With an emulation module

- 1. Create a logic analyzer trigger.

- 2. In the Intermodule Window (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume), select the emulation module icon, then select the analyzer which is intended to trigger it.

- 3. Enable the emulator's "Break In" port "On Rising Edge" (see "Configuring the Emulator" on page 13).

- 4. Select *Run* in the logic analyzer window to start the trace measurement.

- 5. Start processor execution, if necessary.

When the trigger occurs, processor execution should break into the monitor.

### With an emulation probe

- 1. Connect the trigger output to the emulation probe's "Break In" port.

- 2. Enable the "Break In" port configuration option.

- 3. Start the trace measurement. When the trigger occurs, processor execution should break into the monitor.

4. Start processor execution.

This type of coordination lets you break processor execution on more specific conditions than are provided by breakpoints. For example, you can trigger and break on the write of a particular value to a particular address.

### See Also

- To enable or disable emulator break on trigger (see the *Listing Display Tool* help volume).

- To trigger after, about, or before a source line (see the *Listing Display Tool* help volume).

- The processor solution manual for your processor (if available).

# To trigger an analyzer on a break

If you want to trace execution that occurs before a break:

#### With an emulation module

- 1. Configure the "Trigger Out" port to be high when processor execution is in the monitor (see "Configuring the Emulator" on page 13).

- 2. Set the logic analyzer to trigger on *anystate*.

- 3. Set the trigger point to center or end.

- 4. In the Intermodule Window (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume), select the logic analyzer you want to trigger, then select the emulation module.

The logic analyzer is now set to trigger on a processor halt.

5. Wait for the Run Control window to show that the processor has stopped.

### NOTE:

The logic analyzer will store states up until the processor stops, but will continue running. When the processor stops, you may see a "slow clock" message, or the logic analyzer display may not change at all.

6. In the logic analyzer window, select *Stop* to complete the measurement.

## With an emulation probe

- 1. Connect the emulation probe's "Trigger Out" port to the analyzer's input port.

- 2. Configure the "Trigger Out" port to either be high or low when processor execution is in the monitor (see "Configuring the Emulator" on page 13).

- 3. Configure the logic analyzer's input port. For example, if "Trigger Out" is low when in the monitor, configure the analyzer to look for a falling edge.

- 4. Set up the analyzer to trigger on the input signal (storing states that occur before the trigger).

- 5. Start the trace measurement.

- 6. Start processor execution. When the break occurs, the analyzer should trigger.

# To omit monitor cycles from the trace

If you have an emulation probe, you can omit monitor cycles from a logic analyzer trace by using the "Trigger Out" port signal as an analyzer clock qualifier. That is, the analyzer is only clocked when processor execution is outside the monitor.

- 1. Connect the emulation probe's "Trigger Out" port to the analyzer's clock qualifier input.

- 2. Configure the "Trigger Out" port to either be high or low when processor execution is in the monitor (see "Configuring the Emulator" on page 13).

- 3. Configure the logic analyzer's clock qualifier input. For example, if "Trigger Out" is low when in the monitor, configure the analyzer to clock only when the qualifier input is high.

- 4. Set up and start analyzer trace measurements normally. The processor must be executing user code (not executing in the monitor) in order for data to be clocked into the analyzer.

# To open windows

The Emulation Control Interface gives you several ways to open new windows:

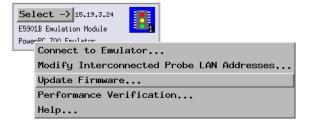

## **Opening windows from the Emulation Control Interface icon**

- 1. Move the mouse cursor over the Emulation Control Interface icon in the system window or in the workspace window.

- 2. Press and hold the right mouse button.

- 3. Move the mouse cursor over the menu selection for the window you wish to open.

- 4. Release the right mouse button.

```

Select. -> 15.19.3.24

E50 Disconnect from Emulator...

Run Control...

Load Executable...

Breakpoints...

Registers...

Memory...

I/O...

Memory Disassembly...

Status/Error Log...

Command Line...

Setup...

```

## Opening windows from the Window menu

- In any emulation window menu bar, select *Window*.

- Select the emulator.

- Select the window you want to open.

### **Creating and naming new windows**

You can open several copies of certain windows, such as the Memory window.

1. In the menu bar, select File then select New Window. The new window

will be given a number, such as Memory <<3>>.

2. (Optional) In the new window, select *File* then select *Rename*. Enter a new name for the window and select *OK*.

The new window can be opened from the Emulation Control Interface icon or from the Window menu.

# To close windows

• In the menu bar, select *File* then select *Close*.

## Auto-close

You can turn on Auto-close so that when you select a new window from the *Window* menu, the current window will be closed. To turn on Auto-close, select *Window* in the menu bar, then select *Auto-Close [ON]*.

## **Deleting windows**

When you create a new window using *File->New*, the window will still be listed in the *Window* menu after you have closed it. To delete the window from the list, open the window then select *File->Delete*.

# Managing Run Control Tool Windows

- "To open windows" on page 51

- "To close windows" on page 52

- "To use the Status/Error Log window" on page 53

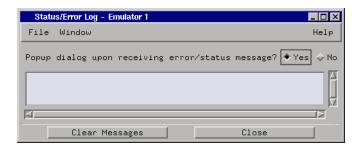

# To use the Status/Error Log window

The Status/Error Log window is the central repository for error and status messages.

To specify when the Status/Error Log window appears:

1. Open the Status/Error Log window.

- 2. If you want the Status/Error Log window to automatically appear every time an error or status message occurs, select *Yes* for *Popup dialog upon receiving error/status message?*. If you only want the Status/Error Log window to appear when you open it, select *No*.

- 3. Close the Status/Error Log window.

Clear Messages empties the contents of the Status/Error Log window.

See Also

"Error/Status Messages" on page 60

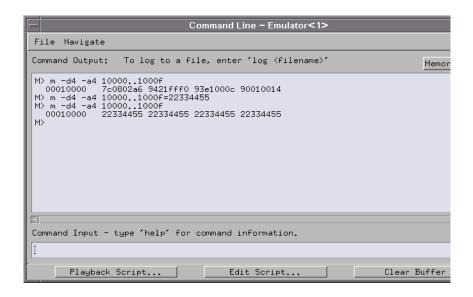

## To Use the Command Line Interface

- 1. Open the Command Line window.

- 2. Enter commands in the Command Input field.

The help command provides command syntax and other information. For example, for help on the m command, enter the help m command.

Enter comments by beginning a line with the # character.

- 3. Each line begins with a status prompt, such as M> or U>.

- M> indicates your target system is in the debug mode, not running user code.

- U> indicates your target system is running user program code.

For definitions of all of the status prompts you might see in the Command Line window, type, *help proc*.

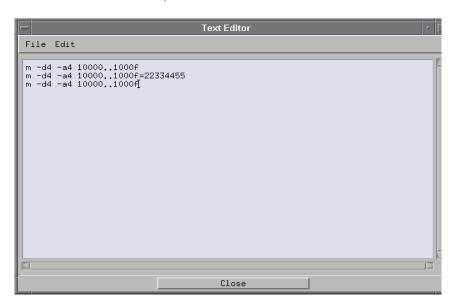

The command line interface is useful, for example, for creating scripts that initialize the target system to a known state. For example, scripts can set initial register or memory values or write an I/O sequence.

*Playback Script* will execute commands that have been saved in a script file.

*Edit Script* opens a simple text editor that lets you enter and save a sequence of commands in a file.

Clear Buffer clears the Command Output buffer.

*Memory Test...* displays the Memory Test window where you can determine the condition of your target system memory hardware.

Use the up and down arrow keys to scroll through a list of the last 20 commands which you have entered.

Use the log (see page 56) command to save command line output to a file.

## **Example**

To create a script that reads a range of memory addresses, writes

22334455 to those addresses, and then reads the memory address range again:

- 1. Select Edit Script.

- 2. In the Text Editor window, enter the commands:

- 3. Select the *File->Save* command from the menu bar, enter the name of your file in the File Selection dialog, and select *OK*.

- 4. Close the Text Editor window.

To play back the script just created:

- 1. Select Playback Script.

- 2. Select the name of the probe configuration settings script file in the File Selection dialog, and select *OK*.

The output will look similar to the following:

## **Managing Run Control Tool Windows**

### Limitations

- Some of the commands listed when you type help are not available. In particular, the pv and init commands cannot be used.

- In *demo mode*, commands entered in this window (including the help command) have no effect.

- "To save command line output in a log file" on page 56

- "To create a script from a log file" on page 57

- "To cancel a command" on page 57

- "Timouts in the Command Line window" on page 58

- "Commands not available in the Command Line window" on page 58

- "Testing Target System Memory" on page 68

# To save command line output in a log file

- In the Command Line window, enter the log filename command.

Enter the full path for the log file.

- 2. Enter commands or playback a script. The commands and their output will

## See Also

be saved to the file.

3. To stop logging to the file, enter the log off command.

## **Example**

To save the values of all of the registers to the file "reglog01.log" enter:

```

log /logic/mylogs/reglog01.log

reg

log off

```

## To create a script from a log file

- 1. Select Edit Script.

- 2. Select *File->Load Script*, then choose the log file.

- 3. Edit the text to remove:

- the ">" prompt

- the output of the command

- the "Logging to" line

- the "Logging turned off" line

- 4. Save the script.

## To cancel a command

Select the *Cancel* button in the Busy dialog to cancel the currently executing command.

Commands that create no output cannot be cancelled and will cause the connection to the emulation probe to timeout (see page 58).

If you use the **rep** command to write a loop, make sure that there is a command in the loop which will generate some output.

For example, rep 0 {m 0..100=0} will repetitively write 0 to the entire memory range 0..100. Because the maddress=value command produces no output, the command cannot be cancelled. By changing the command to rep 0 {m 0..100=0;echo .} a dot is written after every complete write of the range 0..100 and you will be able to

cancel the command.

## **Timouts in the Command Line window**

Timeout is one minute.

Every command must generate output that occurs at a rate of at least once a minute. Faster rates of output are desirable. For example, the command **w 70** (wait 70 seconds) will cause the system to timeout and should not be used. In addition, commands like **m 0..10000=0** which fill large segments of memory may cause the system to timeout. Use *Memory Fill* in the Memory Window to fill memory.

## Commands not available in the Command Line window

Some of the commands listed when you type help in the Command Line window are not available.

The unavailable commands are:

- cf\_var

- cfsave

- cl

- dump

- end

- init

- lan

- load

- mo

- po

- pv

- sio

- sioget

- sioput

# Chapter 1: Using the SH7750 Emulation Control Interface Managing Run Control Tool Windows

- slist

- start

- stty

- ureg

# Error/Status Messages

Select the messages below for additional information on some of the error/status messages that can occur when using the Emulation Control Interface.

The following messages can appear in either the Error/Status Log window or in the Command Line Interface window.

Debug Mode Access Error (see page 61)

Debugger: memory update (see page 61)

Debugger: register update (see page 61)

Hardware breakpoint (see page 62)

Memory access failed (see page 62)

Software breakpoint (see page 62)

Stepping failed (see page 62)

Target power is off (see page 63)

Unable to break (see page 63)

Unable to modify register: PC=value (see page 63)

Unknown break cause (see page 63)

Unimplemented opcode/register (see page 63)

The following error messages appear in the Breakpoint window:

Address is a duplicate of Breakpoint #\_ (see page 61)

Address is not on an instruction (4-byte) boundary (see page 61)

Enable breakpoint failed (see page 62)

"To use the Status/Error Log window" on page 53

See Also

# Address is a duplicate of Breakpoint #\_

This error occurs if you try to set a breakpoint at an address which already has a breakpoint. Only one breakpoint is allowed at a given address.

# Address is not on an instruction (4-byte) boundary

This error occurs if the address ends in a hexadecimal digit other than 0, 4, 8, or C. Breakpoints can only be set on 4-byte instruction boundaries.

# Debug Mode Access Error

This error occurs if there has been a communication error between the emulator and the target system.

Try the operation again. If the error occurs again, check all connections. If the emulator is connected directly to the target board (through a target interface module), check that the target's debug port meets the guidelines in the emulator *Installation and Service Guide*.

# Debugger: memory update

This message occurs when target system memory has been modified by another external connection (presumed to be a debugger).

# Debugger: register update

This message occurs when a processor register has been modified by

another external connection (presumed to be a debugger).

# Enable breakpoint failed

This error occurs if an attempt to write a software breakpoint at the indicated memory address failed. If you are setting a software breakpoint, check that the address is in RAM, not ROM.

# Hardware breakpoint

This message occurs when the processor has stopped at a hardware breakpoint at the specified address.

# Memory access failed

This error occurs if the processor was unable to access memory (processor-generated exception).

# Software breakpoint:

This message occurs when the processor has stopped at a software breakpoint at the specified address.

# Stepping failed

This error occurs if the step command was unsuccessful because attempt to write to the program counter failed.

# Target power is off

This error occurs if the emulator detects that power is off on the target processor.

## Unable to break

This error occurs if the processor does not return a status message to the emulator indicating that it has stopped.

# Unable to modify register: PC=value

This error occurs if a register command was unsuccessful because attempt to write to the program counter failed.

## Unknown break cause

Something other than the emulator caused a break. Possible causes include a "break" button on the target system, a trap instruction, or noise in the target system circuitry.

# Unimplemented opcode/register

This error occurs if the processor tried to execute an illegal instruction (processor-generated exception).

# SH7750 Run Control Tool—New Features in This Version

• This is the first version of the SH7750 Run Control tool.

# To update firmware

Update the firmware if:

- The emulation module or emulation probe is being connected to a new analysis probe or *TIM*, or

- The emulation module was not shipped already installed in the logic analysis system, or

- You have an updated version of the firmware.

### To install firmware from a CD-ROM to the hard disk

• Follow the instructions printed on the CD-ROM jacket.

This will install the firmware onto the logic analysis system hard disk. Continue with either the "To update emulation module firmware" or the "To update emulation probe firmware" instructions.

## To update emulation module firmware

- 1. End any emulation sessions that may be running. Remove any emulation module icons from the workspace in the Workspace window.

- 2. Install the firmware onto the logic analysis system's hard disk, if necessary.

- 3. In the system window, select the emulation module and select *Update Firmware*.

4. In the Update Firmware window, select the firmware version to load.

Select the  $Additional\ Information$  button to display additional information about the firmware you selected.

### To update firmware

5. Select *Update Firmware*.

## To update emulation probe firmware

- 1. End any emulation sessions that may be running.

- 2. Install the firmware onto the logic analysis system's hard disk, if necessary.

- 3. In the workspace window, drag the emulation probe icon onto the workspace.

- 4. Select the emulation probe icon and select *Update Firmware...*.

- 5. In the Update Firmware window, enter the LAN name or address of the emulation probe.

- 6. In the Update Firmware window, select the firmware version to load.

Select the *Additional Information* button to display additional

- information about the firmware you selected.

- 7. Select *Update Firmware*.

- 8. Cycle power on the emulation probe.

## To display the current firmware version

• Select *Display Current Version* to see what firmware version is already installed in your emulation module or emulation probe.

### To install firmware from another source

If you obtained firmware from another source, such as from an ftp server or a World Wide Web site: //www.agilent.com/find/sw-updates

- Follow the instructions provided with the firmware, OR

- Copy the firmware files into /logic/run\_cntrl/firmware on the logic analysis system hard disk. Be sure to copy *all* of the files which begin with the product number of the firmware for your microprocessor.

# Disconnecting from the Emulator

- 1. Select the Emulation Module icon or Emulation Control Interface icon and then select  $Disconnect\ from\ Emulator.$

- 2. In the Connect Emulator window, select  $Disconnect\ from\ Emulator.$

# **Testing Target System Memory**

Many times when a system under test fails to operate as expected, you will need to determine whether the failure is in the hardware or the software. These tests verify operation of the memory hardware in the system under test.

## **To Test Target System Memory**

- 1. Open the Memory Test window (see page 83).

- 2. Specify the Memory Test (see page 70) to be performed.

- 3. Specify the Memory Range (see page 82) to be tested.

- 4. Specify the Data Value (see page 82) to be used when performing the test.

- 5. Specify the Options (see page 82), number of times the test is to be repeated and type of error message information to be presented during the test.

- 6. Open the Command Line window if it's not already open.

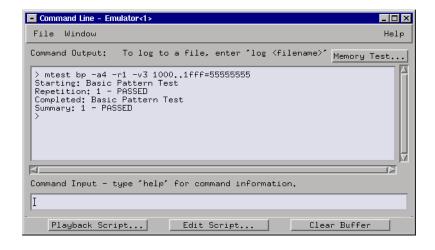

- 7. Select the *Execute Test* button.

- 8. View test results in the Command Line window.

The Command Input line in the Command Line window will show the equivalent terminal interface command during each test.

The Busy dialog box appears while the test executes. It also shows the equivalent terminal interface command during each test. A *Cancel* button in the Busy dialog box can be used to stop a test in progress.

To check untested memory hardware, follow the "Recommended Test Procedure" on page 83.

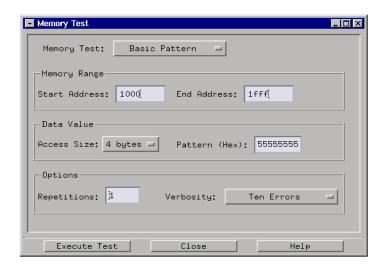

### Example

The following example writes the value "55555555" to addresses 1000 through 1fff (hexadecimal). Then it compares the values in memory with the values that were written. Next, the test writes the compliment "aaaaaaaa" to the same range of addresses and compares the new

values in memory with the values that were written.

- 1. Open the Command Line window and select the *Memory Test* button.

- 2. In the Memory Test window, specify the memory test shown below.

- 3. Select the Execute Test button.

- 4. View the test results in the Command Line window.

See Also

• "Recommended Test Procedure" on page 83

# **Memory Test:**

The Memory Test feature of the Emulation Control Interface can perform seven different types of tests. Use these tests to find problems in address lines, data lines, and data storage. Use these tests in combination because no single test can perform a complete evaluation of the target system memory.

### Basic Pattern

- Use this test to validate data read-write lines.

- "To perform the Basic Pattern test" on page 71

- "How the Basic Pattern test works" on page 72

### Address Pattern

- Use this test to validate address read-write lines.

- "To perform the Address Pattern test" on page 73

- "How the Address Pattern test works" on page 74

### Rotate Pattern

- Use this test to validate data read-write lines, and test voltage and ground bounce.

- "To perform the Rotate Pattern test" on page 74

- "How the Rotate Pattern test works" on page 76

## Walking Ones

- Use this test to validate individual storage bits in memory.

- "To perform the Walking Ones test" on page 77

- "How the Walking Ones test works" on page 77

### Walking Zeros

- Use this test to validate individual storage bits in memory.

- "To perform the Walking Zeros test" on page 78

• "How the Walking Zeros test works" on page 79

## Oscilloscope Read

- Use this test to generate the signals associated with reading from memory so they can be viewed on an oscilloscope.

- "To perform the Oscilloscope Read test" on page 79

- "How the Oscilloscope Read test works" on page 80

## Oscilloscope Write

- Use this test to generate the signals associated with writing to memory so they can be viewed on an oscilloscope.

- "To perform the Oscilloscope Write test" on page 80

- "How the Oscilloscope Write test works" on page 81

# To perform the Basic Pattern test

- 1. Open the *Memory Test* dialog box from either the Memory window or the Command Line window.

- 2. In the *Memory Test* dialog box, select the *Basic Pattern* Memory Test.

- 3. Type in the *Memory Range* to be tested.

- 4. Select the *Access Size* to be written, and type in the *Pattern* to be written.

- 5. Set *Repetitions* to 1. This causes the test to be performed one time.

- 6. Set *Verbosity* to *Ten Errors*. This is the recommended verbosity for the first test in a series of tests.

- 7. Select the *Execute Test* button.

- 8. When the test is complete, the Command Line window will show the test results. Error messages will be shown if any errors were found during the test.